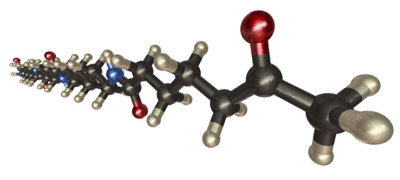

Figure 1. Cross-section from the Unimicron process from reference [1].

The last post discussed the dry film EMC using a printed circuit board vacuum lamination approach. The panel size was 508 mm x 508 mm [1]. Panel level processing will ultimately result in lower cost per unit.

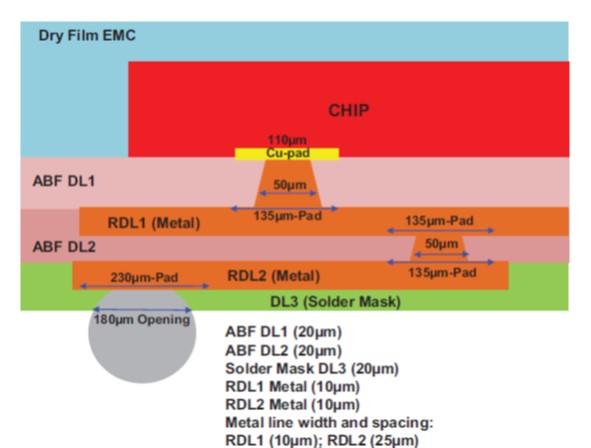

What will be some of the major technical challenges? The epoxy molding compound (EMC) encapsulation process will need to be optimized for a panel format. Liquid EMC will be difficult to process in the panel format since new tools will be required and achieving uniform thickness across a large panel will be difficult. In response to the need for a panel level EMC, several EMC suppliers have developed EMC in sheet form. As shown in Figure 2, Hitachi Chemical has developed an embedded insulation resin for chip sealing called EBIS.

Figure 2. Film-based epoxy mold compound for FOWLP (source: Hitachi Chemical)

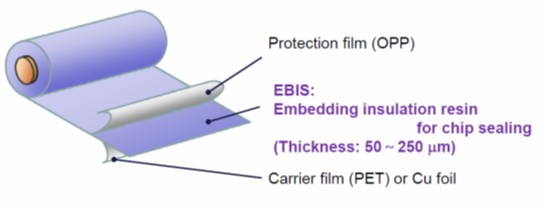

In this form, the highly-filled epoxy base resin is coated onto a carrier in thicknesses ranging from 50 – 250 µ). The EMC film is used in a vacuum lamination process to encapsulate the chips on the re-constituted wafer or panel. Ajinomoto Fine-Techno has also developed two types of epoxy mold compounds; liquid EMC (called the MI Series) for wafer level fan-out packages and a film EMC (called the LE Series) for the panel level fan-out process.

Figure 3. Two types of epoxy molding compounds for fan-out packaging (source: Ajinomoto Fine-Techno LTD)

From the table in Figure 3, the glass transition temperature (Tg) is in the range typical of cured EMC. One property to note is that for the FOWLP process, the coefficient of thermal expansion (CTE) needs to be very low and is usually matched to the CTE of the carrier. Note that the CTE reported in Figure 3, is identified as the CTE below the glass transition temperature. I also like the details provided which indicate the Tg was measured using dynamic mechanical analysis (DMA) and the CTE reported was over the temperature range of 30-150°C. The major driver for lowering the CTE and modulus is to reduce warpage after EMC processing either in the wafer or panel process.

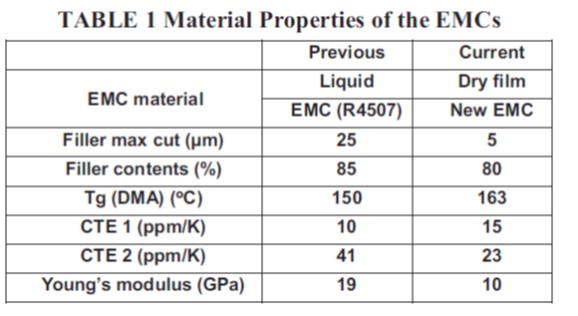

In the last post, data was presented for a new film-based epoxy mold compound used in the Unimicron process. For ease of comparison, the data is presented in Table 1 (from reference [1]).

There are a couple key property differences in the two approaches. First the CTE below Tg (CTE 1 in Table 1) for the Unimicron dry film EMC is 15 ppm/°C which is nearly double the CTE for the Ajinomoto LE series. The CTE of the EMC is typically closely matched to the CTE of the carrier. In the Unimicron process, the carrier likely has a CTE in the range for printed circuit boards. The 15 ppm/°C for the CTE 1 makes sense. If the panel uses a glass substrate (or other ceramic) with the Ajinomoto LE EMC, then the lower CTE 1 of 7 ppm/°C is appropriate. Note that the modulus of the two film-based EMC’s are about the same; 7 GPa for the Ajinomoto LE series and 10 GPa for the dry film EMC in the Unimicron process. Another similarity is the Tg’s are very close; 167°C for the Ajinomoto LE series and 163°C for the dry film EMC in the Unimicron process.

References

- John Lau et. al. “Feasibility Study of Fan-Out Panel-Level Packaging for Heterogeneous Integrations, 2019 IEEE, 69th Electronic Components and Technology Conference. The authors were part of a consortium consisting of the following companies; Unimicron, ASM Pacific Technology Ltd, Dow Chemical Company, Jiangyin Changdian Advanced Packaging Co., Ltd., Indium Corporation, Huawei Technologies Co. Ltd., Hong Kong University of Science and Technology.

Leave a Reply