The last post described some of the new developments in film-based epoxy mold compounds from Hitachi Chemical (EBIS) and Ajinomoto (see image above courtesy of Ajinomoto Fine-Techno). The main driver for panel level processing is to reduce cost. Another area where there is an opportunity to reduce cost is in the redistribution layer process. The main dielectrics used in wafer-based fanout is photosensitive polyimides and polybenzoxazole (PBO) positive tone resists. A commonly used positive tone photosensitive PBO is HD8940 (Hitachi DuPont). A challenge has been to lower the cure temperature of the PBO and polyimides to be less harsh on the epoxy mold compounds.

High temperature processing of the photosensitive dielectrics will be an even bigger challenge in panel level processing. The panel process will initially use a printed circuit board type process flow which entails lower temperature processes. With this in mind, Dr. John Lau at ASM Pacific has been leading a consortium investigating panel level processing. The consortium includes ASM, Dow, Huawei, Indium, JCET and Unimicron. The team recently published an interesting paper describing the printed circuit board approach to panel level fanout [1]. The paper demonstrates several concepts that will be important for panel level processing:

- Dry film epoxy mold compound

- Build up films used as dielectrics for redistribution layers (RDL1 and RDL2)

- Heterogeneous integration of 4 chips into the fanout package

- Demonstration of a new assembly process called uni-substrate-integrated-package (Uni-SIP)

- Printed circuit board processes like electroless copper seed layer, laser direct write imaging and circuit board copper plating processes are used

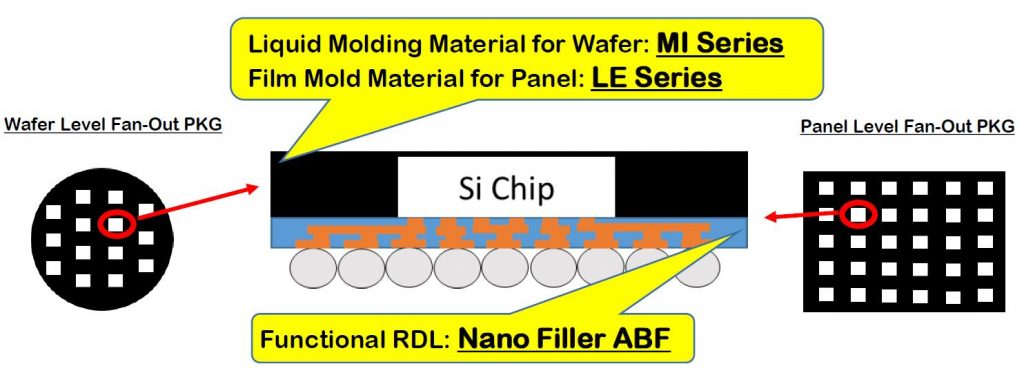

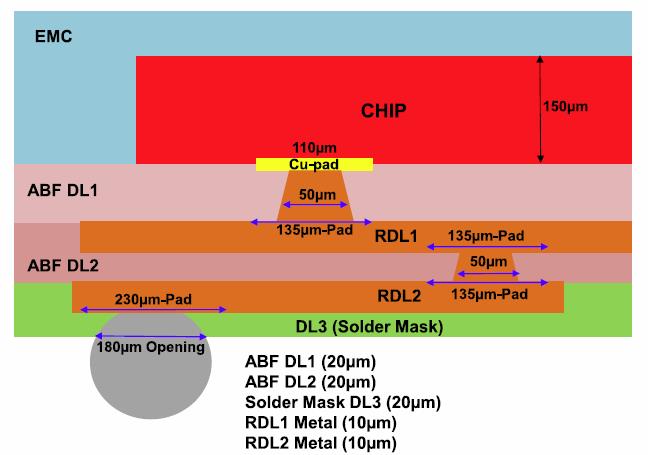

The Uni-SIP process used Ajinomoto Build Up Films (ABF) for the redistribution layers. The cross-section of the package is shown in Figure 1.

Figure 1. Cross-section of package build using the Uni-SIP process (image from reference [1])

In this case, a liquid epoxy mold compound from Nagase (R4507) was used in a modified compression molding process. The EMC had high filler loading (85%) and a Tg of 150°C (DMA). The CTE below Tg was 10 ppm/K. The redistribution layers were fabricated using Ajinomoto Build Up Films.

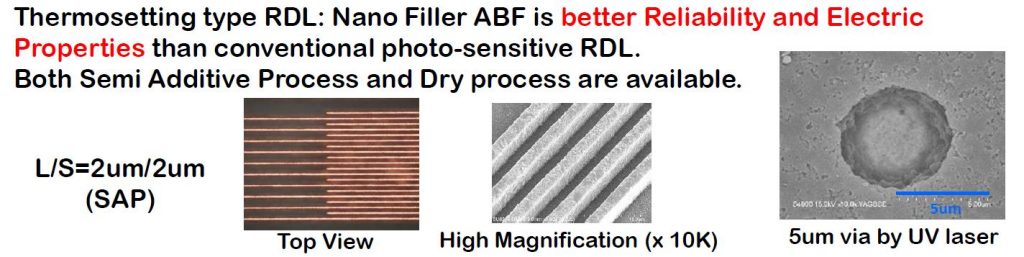

Figure 2 shows the attributes of the ABF type of RDL (courtesy of Ajinomoto Fine-Techno). The ABF films are negative tone materials, that is they crosslink under UV exposure and thus the exposed area is rendered insoluble. Recall that positive tone PBO and PI RDL dielectrics become soluble under UV exposure, the opposite of a negative tone resist.

Figure 2. Characteristics of Ajinomoto Build Up Films used for redistribution layers in a panel level process (courtesy of Ajinomoto Fine-Techno).

In Figure 2, the optical photograph shows the ABF approach is capable of 2 µ lines and spaces and 5 µ diameter UV laser drilled vias. The ABF dielectric layers are vacuum laminated onto the panel using printed circuit board methods.

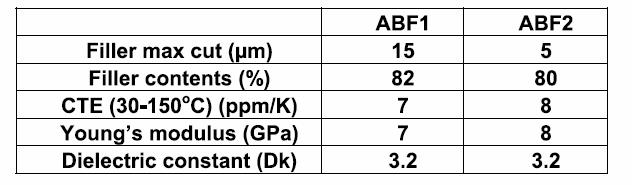

The properties of the ABF layers are shown in the following table from reference [1].

The Ajinomoto build-up film RDL layers are highly filled (80-82% loading) resulting in a low CTE in the range of 7-8 ppm/K. Note that this is very close to the CTE of the Nagase R4507 epoxy mold compound. The dielectric constant is important in the RDL since the signal speed will be impacted by the Df of the RDL layer.

A future post will cover the recent advances in build up films from both Ajinomoto and Sekisui.

References:

1 John Lau, et. al., Chip-First Fanout-Out Panel-Level Packaging for Heterogeneous Integration, IEEE Transaction on Components, Packaging and Manufacturing Technology, Vol. 8, No. 9, September 2018, p. 1561

Leave a Reply