In this post we return to polymers in electronic packaging. In October there were two electronic packaging conferences. The International Microelectronics Assembly and Packaging Society (IMAPS) national conference was held in Pasadena, CA on October 8-11. The second conference was the International Wafer Level Packaging Conference (IWLPC) which is held every year in San Jose. This year the IWLPC was held on October 23-25. The most exciting topics of discussion at both of these conferences was Fan-Out Wafer Level Packaging. Earlier in the year I had a couple introductory posts on Fan-Out Wafer Level Packaging [1, 2].

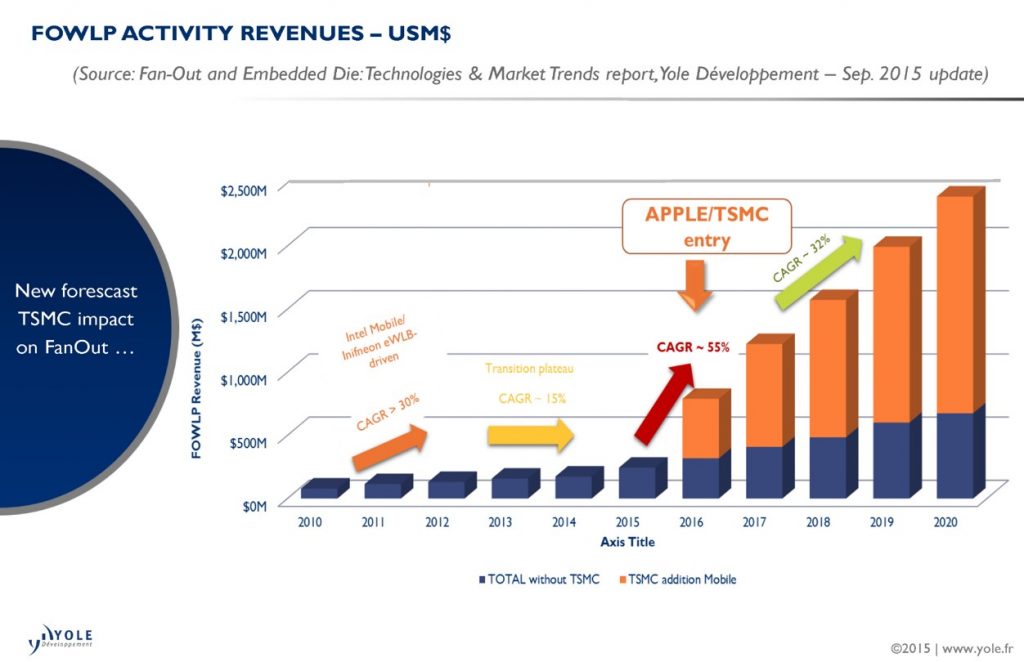

Let’s start with a quick update on the current status of wafer level packaging (WLP). Wafer level packaging has transitioned from “powerpoint engineering” to volume production. The key event in the explosion of eWLP was the announcement that Taiwan Semiconductor Manufacturing Corporation (TSMC) was going to package the Apple A10 processor using TSMC’s InFO (Integrated Fan Out). The large impact of the TSMC entry is shown in Figure 1 (source: Yole Developpement).

Figure 1. FOWLP revenues as a function of time (years)

Note in Figure 1 that the Apple share currently dominates the FOWLP production volumes from 2016 out to 2020. While there is healthy growth for the rest of the FOWLP packagers (blue portion in Figure 1), the volumes are much smaller. It should be noted this data is a bit dated, but I use it to demonstrate the market trends.

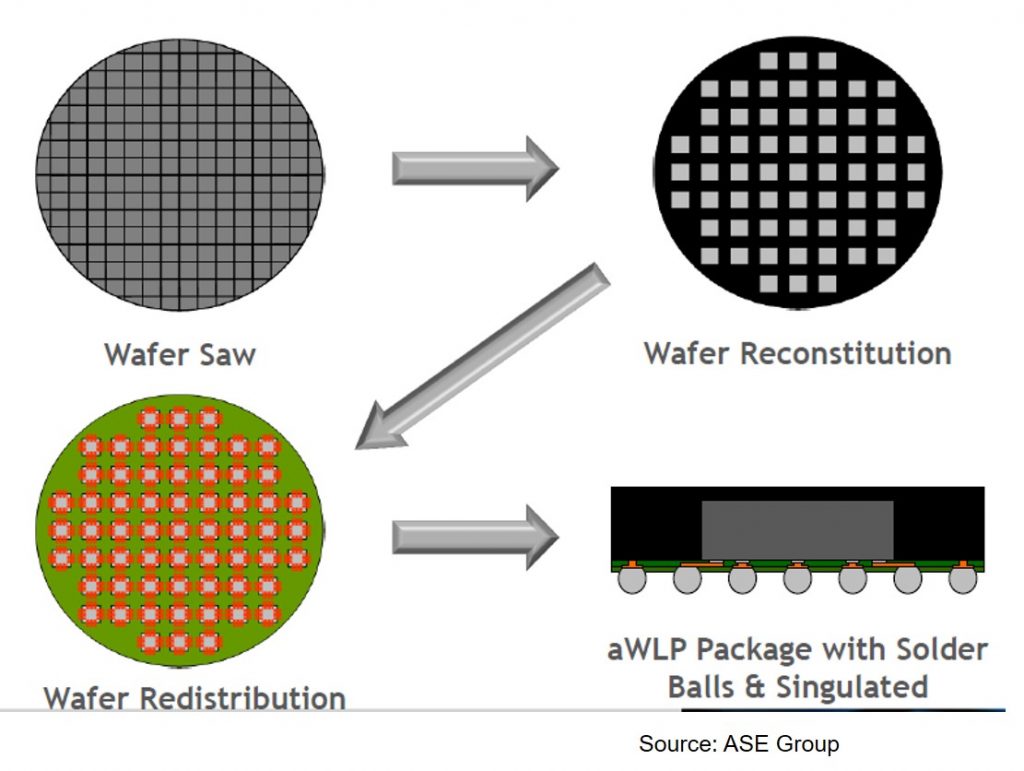

To review, the original FOWLP was developed to leverage the wafer fab equipment and processes. The first FOWLP was done on circular 200 mm wafers, but quickly transitioned to 300 mm wafers to use the existing equipment set for that size wafer. To date, most of the materials have been developed for 300 mm wafer processes (mold compounds, redistribution layers, temporary bonding adhesives). A high level overview of the FOWLP process flow for 300 mm round wafers is shown in Figure 2.

Figure 2. Fan-Out Wafer Level Process for 300 mm wafers (Source: ASE Group)

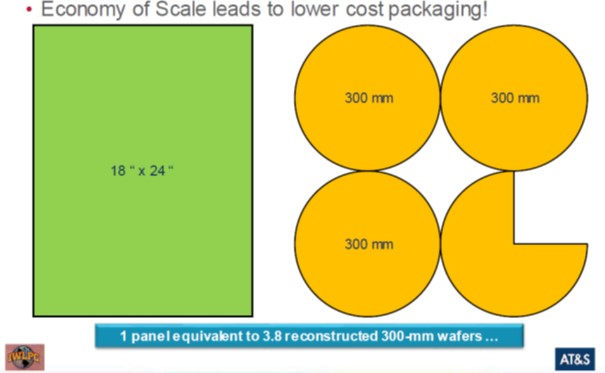

In anticipation of future volume ramps, many packagers started thinking about how to reduce cost. For high-end chips (like the Apple A10 or A11) the wafer format will yield the best results in terms of yield and technology (smaller lines and spaces, more density, etc). For low-end FOWLP such as used in mobile phones, cost will be an important driver. In order to reduce cost, several packagers in the industry have started to evaluate making the FOWLP on a panel format. The panel format is commonly used in the printed circuit board (PCB) and semiconductor substrate manufacturing process. The typical panel size in the PCB industry is 18 inches X 24 inches.

Chet Palesko from SavanSys presented a paper at the 2014 IWLPC conference where he presented data on the cost structure of panel versus wafer. His data indicated the following:

- 300 mm wafer yields 616 10 mm x 10 mm packages

- 400 mm x 500 mm panel yields 1,911 10 mm x 10 mm packages

To graphically illustrate the panel versus wafer production scale, AT&S (PCB producer, and thus used standard 18 x 24 inch panels) showed the following comparison in Figure 3.

Figure 3. Panel versus wafer for FOWLP (Source: AT&S)

In Figure 3, one 18 x 24 inch panel is equivalent to 3.8 reconstituted 300 mm wafers which is similar to the 3.1 ratio SavanSys presented in the case of the 400 x 500 mm panel size (slightly smaller panel). At the most recent electronic packaging conferences, there were panel discussions on “panels.” While most of the details are closely held, there is consensus that at some point in the future (likely around 2020) panel formats will be widely available from several packagers. On the other hand, TSMC will likely to continue to use the wafer format for the InFO process since it is integrated into the back end of the wafer fab process.

The next few posts will cover additional recent developments in the area of FOWLP.

References:

Leave a Reply